Laporan Akhir 2 Percobaan 4

1. Jurnal [back]

2. Alat dan Bahan [back]

- LED

- Switch

- JK Flip Flop

- D Flip Flop

- Clock

1.

Bagaimana

jika B0 dan B1 sama sama diberi logika 0, apa yang terjadi pada rangkaian?

Outputnya

berupada LED ,dimana kalau BO dan B1 berlogika 0 maka semua LED akan hidup karena

kaki flip –flop aktif rendah ( B0 terhubung dengan kaki R dan B1 terhubung dengan kaki S ).

2.

Bagaimana

jika B3 diputuskan/tidak dibubungkan pada rangkaian apa yang terjadi pada rangkaian?

Jika B3 diputuskan semua output berlogika 0 dan semua lampu

LED akan menyala sebagai indicator outputnya

3.

Jelaskan

apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang

pada flip flop?

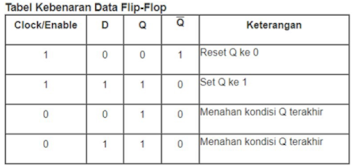

Toggle : Togel dapat

di artikan sebagai output yang berubah terhadap input yang bergerak dari 1 ke

0, bila tidak ada tanda seperti itu maka dapat di artikan output berubah

terhadap input bergerak dari 0 ke 1.

Not change : output

pada not change yang dihasilkan itu bernilai sama (11,00)

Kondisi terlarang :yaitu masukan

nya yaitu R atau S bernilai sama sama logika satu

Tidak ada komentar:

Posting Komentar